Kerala PSC Previous Years Question Paper & Answer

Page:13

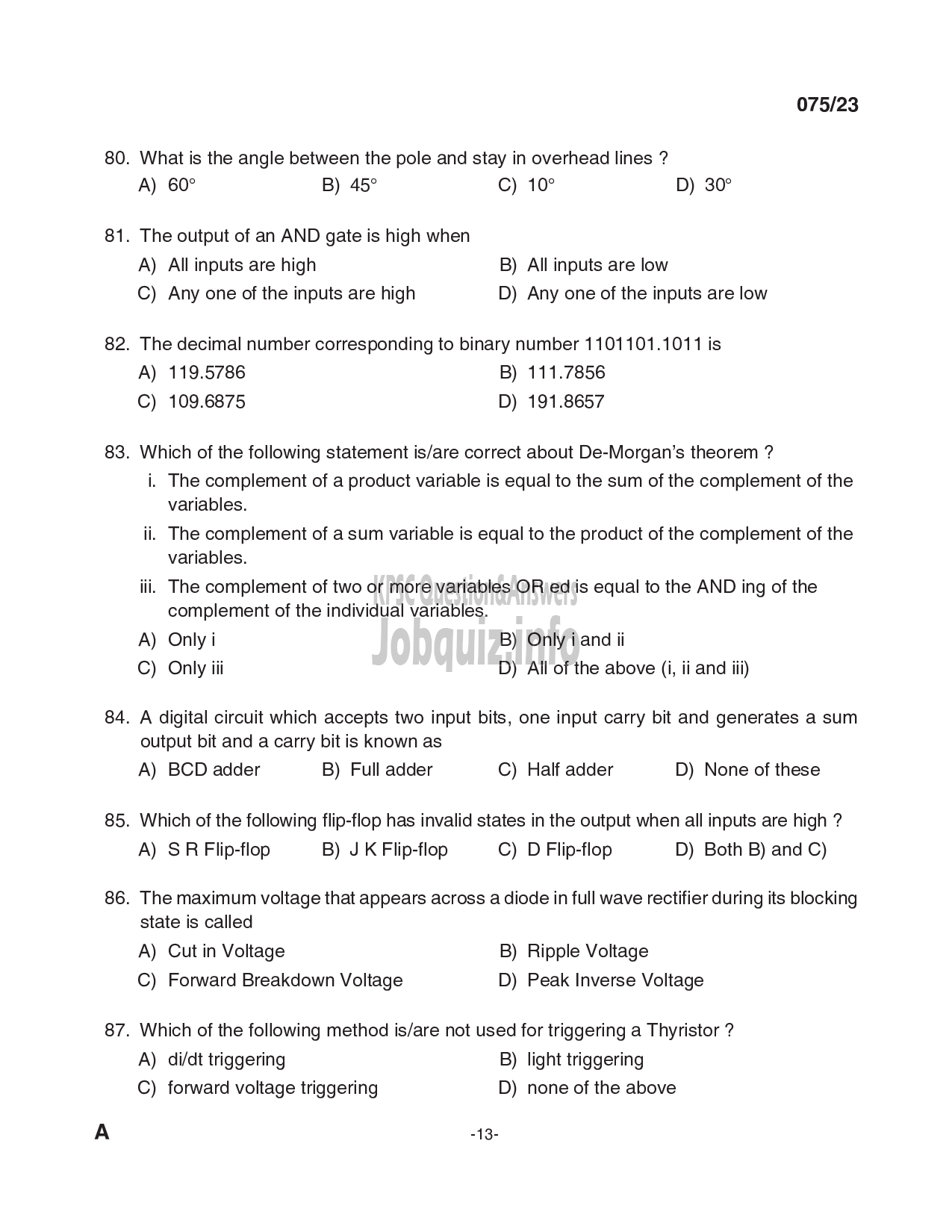

Below are the scanned copy of Kerala Public Service Commission (KPSC) Question Paper with answer keys of Exam Name 'Overseer Gr II (Electrical), Electrician, Workshop Instructor/ Instructor Gr II/ Demonstrator in Electrical Engineering in Universities, KSFDC, Technical Education ' And exam conducted in the year 2023. And Question paper code was '075/2023'. Medium of question paper was in Malayalam or English . Booklet Alphacode was 'A'. Answer keys are given at the bottom, but we suggest you to try answering the questions yourself and compare the key along wih to check your performance. Because we would like you to do and practice by yourself.

80.

81.

82.

83.

84.

85.

86.

87.

075/23

What is the angle between the pole and stay in overhead lines ?

A) 60° B) 45° C) 10° D) 30°

The output of an AND gate is high when

A) All inputs are high B) All inputs are low

C) Any one of the inputs are high D) Any one of the inputs are low

The decimal number corresponding to binary number 1101101.1011 is

A) 119.5786 B) 111.7856

C) 109.6875 D) 191.8657

Which of the following statement is/are correct about De-Morgan’s theorem ?

i. The complement of a product variable is equal to the sum of the complement of the

variables.

ii. The complement of asum variable is equal to the product of the complement of the

variables.

iii. The complement of two or more variables OR ed is equal to the AND ing of the

complement of the individual variables.

A) Onlyi 8) Only i and ii

C) Only iii D) All of the above (i, ii and iii)

A digital circuit which accepts two input bits, one input carry bit and generates a sum

output bit and a carry bit is known as

A) BCD adder B) Full adder C) Half adder D) None of these

Which of the following flip-flop has invalid states in the output when all inputs are high ?

A) SR Flip-flop B) J K Flip-flop C) D Flip-flop D) Both B) and C)

The maximum voltage that appears across a diode in full wave rectifier during its blocking

state is called

A) Cut in Voltage B) Ripple Voltage

C) Forward Breakdown Voltage D) Peak Inverse Voltage

Which of the following method is/are not used for triggering a Thyristor ?

A) difdt triggering B) light triggering

C) forward voltage triggering D) none of the above

-13-